MSMP1 - Low Power SiP

STM32MP1 for IoT Applications

The MSMP1 is the Open Standard Module compliant System-In-Package based on STMicroelectronics STM32MP1 Family architecture offering high-performance single/dual CortexA7 cores in combination with a CortexM4 core. The MSMP1 combines compact design and a wide range of services, bringing low power consumption, thermal efficiency and low-cost to embedded systems.

The STM32MP1 general-purpose microprocessor units (MPUs) are built around two CortexA7 CPU cores. Peripheral functions include support for multiple interfaces, such as Gigabit Ethernet channels, two USB 2.0 channels, and two CAN channels, as well as A/D converter modules, making it ideal for applications such as entry-class social infrastructure gateway control and industrial gateway control. The chosen OSM form factor supports 476 contacts, offers almost all of the CPU functionality on the contacts and is therefore suitable for most industrial applications.

In addition to a wide range of services, the MSMP1 modules also offer new functionalities in terms of flexibility and processing. The OSM Systems-in-Packages can be individually adapted to the respective customer requirements due to four different form factors.

Features

- Single/Dual Cortex-A7, up to 800MHz

- Cortex-M4, up to 209MHz

- 512MB – 1GB DDR3L RAM

- 4GB – 64GB eMMC NAND Flash

- 10/100/1000MBit Ethernet

- USB2.0 Host/OTG

- 2x CAN

- UART, I2C, SPI

- ADC, DAC

- Parallel display port

- Camera interface

- compliant to the SGET OSM standard

- sizeM, 30x45mm

- 476 contacts

- 0°C..+70°C commercial temperature range

- -40°C..+85°C industrial temperature range

Block Diagram

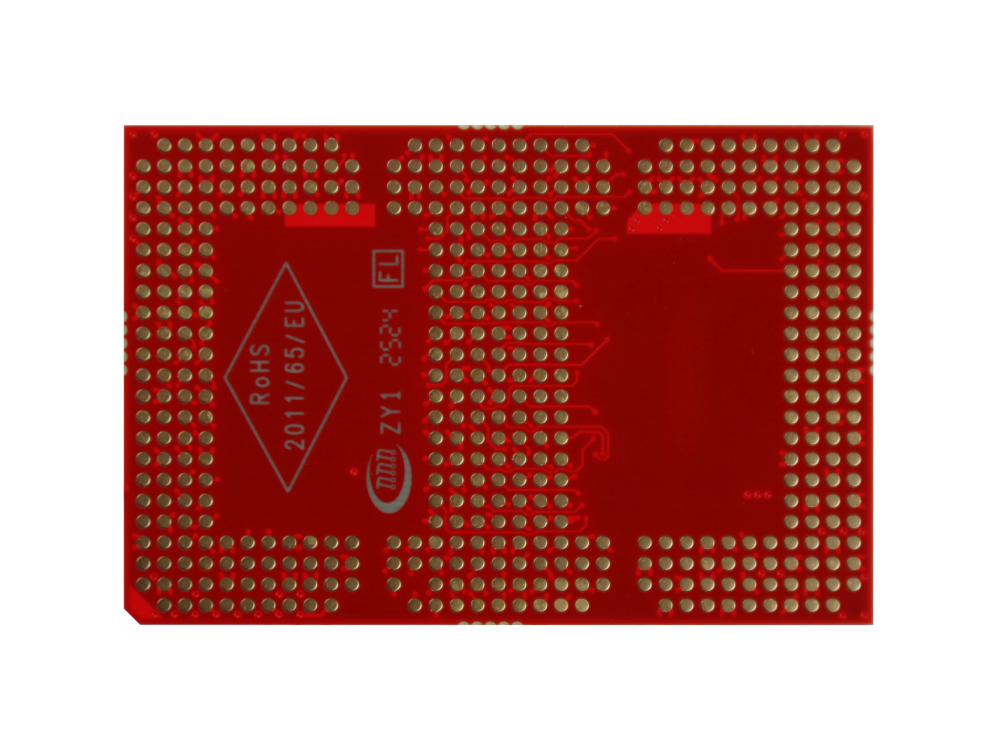

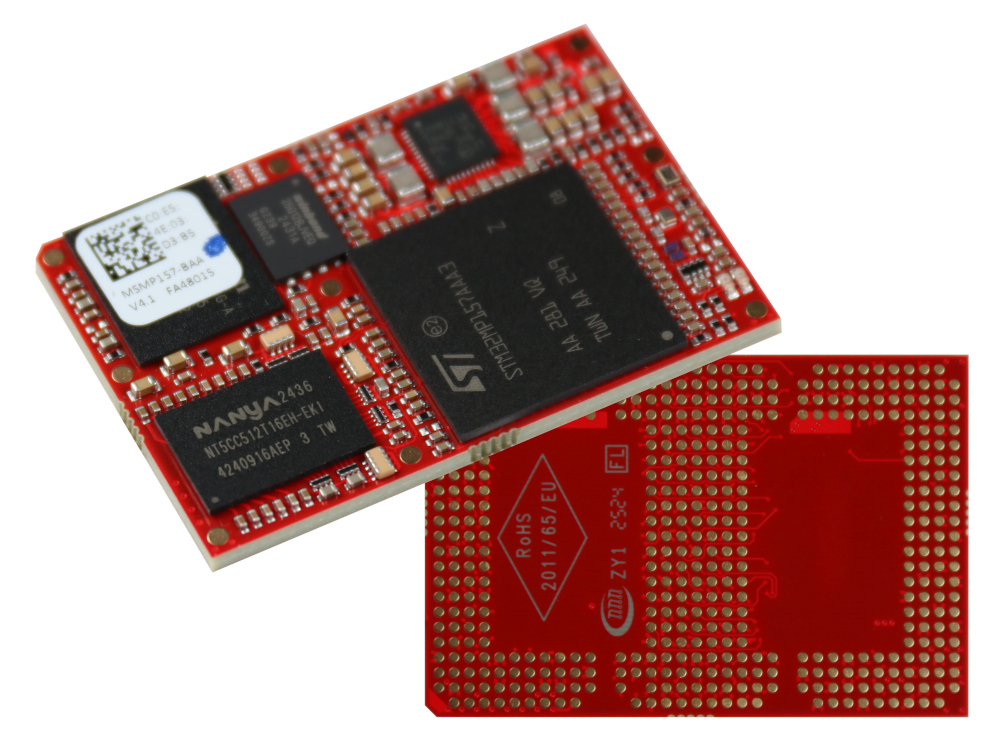

Pictures

Order Codes

MSMP151-A0A

- STM32MP151

- 512MB DDR3L RAM

- no eMMC

- 128MBit SPI NOR

- 0°..+70°C

MSMP157-BAA

- STM32MP157

- 1GByte DDR3L RAM

- 4GB eMMC

- 128MBit SPI NOR

- 0°C...+70°C

OSM Standard |

|

The idea of all Open Standard Modules (OSM) is to create a new, future proof and versatile standard for small-size, low-cost embedded computer modules, combining the following key characteristics:

- different architectures available on the same footprint, scalability in function and performance

- four different mechanical sizes and pin counts, downwards compatible

- pre-defined soft- and hardware interfaces

- specification and design guide publicly available

- design support for baseboard integration, driver development and mass production by ARIES Embedded

- directly assembly to the baseboard without connectors using LGA (Land Grid Array) technology

- completely machine processible during soldering, assembly and testing

The Open Standard Module specification allows developing, producing and distributing embedded modules for the most popular MCU32, ARM and RSICV architectures. For a growing number of IoT applications this standard helps to combine the advantages of modular embedded computing with increasing requirements regarding costs, space and interfaces.